- iPhone topik

- Samsung Galaxy Buds3 Pro - szárat eresztettek a babok

- Változó design, tekerhető lünetta: megjött a Galaxy Watch8 és a Classic

- Hivatalosan is bemutatta a Google a Pixel 6a-t

- Vékonyabb lett, jobb kamerát kapott, de az akku maradt a régi: itt a Fold7

- Xiaomi 15 - kicsi telefon nagy energiával

- Yettel topik

- Garmin Instinct – küldetés teljesítve

- Android alkalmazások - szoftver kibeszélő topik

- Magisk

Új hozzászólás Aktív témák

-

- Az első minták kiszállítva.

- "Nem lesz forradalmi, egy fejlődési lépcső lesz" (saját fordítás a "This won't be a revolution - it will be an evolution"-ra)

- Két memóriavezérlő (bizonytalanok az információk)*

- De marad a két memóriacsatorna

- Nem várható új tuning-technológia, a Curve Optimizer is várhatóan marad a régi.* A két memóriavezérlő jelenthet CUDIMM irányvonalat, de elviekben akár DDR6 vezérlőt is.

-

Csak azt látom, hogy az am4-ről az am5 költsége meg másfélszereződött. Általában a fejlődéssel jár, hogy ugyanazért a pénzért jobb tech-et kapni, ahogy telik az idő, de ott valahogy ez nem érvényesült.

Atx, matx méretben ugyanannyi most egy jó b850 lap, mint egy jó b450 lap volt?

Őőőő....

Mivel a DDR5 és a Gen5 PCI-Express jobb zavarvédelmet kér, mind a DDR4 és a Gen4-es PCI-Express így nem lehet elvárni, hogy a 4 rétegű PCB-kkel is hozza a csúcs teljesítményt az új technológia.

Szóval szerintem szimplán fals elvárásokat támasztasz.

Pont erről szól a hírek oroszlánrésze, hogy az új technológiák gyártása egyre drágább. Legyen szó prociról, memóriáról, flashtárolóról, akármiről. -

válasz

deathcrow42

#20

üzenetére

deathcrow42

#20

üzenetére

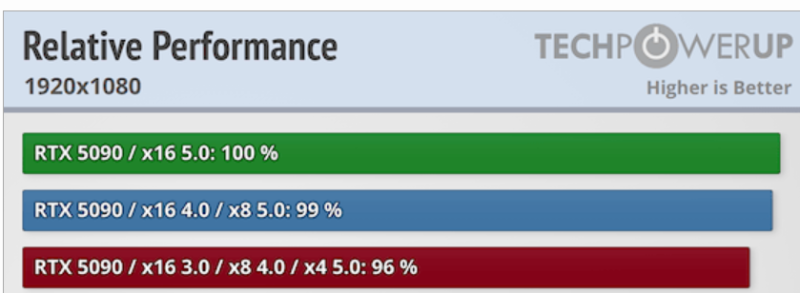

Én azt az oldalt képviselem, hogy legalább a VGA oldalon ne legyen bottleneck az alaplapnál. Ha az aktuális PCIe az 5.0, akkor igenis legyen 16 sáv a VGA-nak

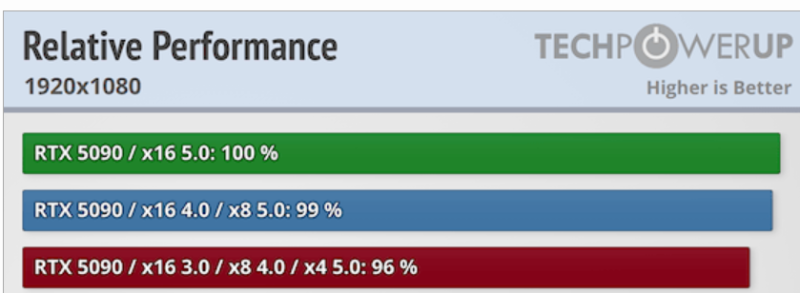

Nagyon átlagolva 1%-os teljesítményvesztés még RTX5090 @1080p esetén is...

Kijöttek a jó kis 8 sávos VGA-k az Nvidiától idén, aztán ha esetleg pcie 3.0-s alaplapba került az 5060, akkor némely esetben olyan borzasztó eredményt hoznak - akár egy 3060-hoz képest is - amivel lassabbak egy 2 generációval előtti azonos kategoriájú vga-nál. mert 8 sávot használ a VGA.

Fordítva nézed az eseményeket.

Ott a Gen3-as PCI-Express a probléma, nem a 8x sáv, és az előbbi ami azért bő 10 éve már lépett. Tehát ez olyan eset, amikor majd jön a Gen7-es PCI-Express (uszkve 6-8-10 év múlva) és akkor kevés lesz a Gen5.Nah és pont emiatt kell ez a júzernek 4 év múlva, ha esetleg bifur miatt az Nvidia 7060 is köhög ebben az alaplapban a 8 sáv miatt, vagy akár egy jövő évi X970-s Zen 6-s alaplapban? Nemááár

A 7060 nem fog köhögni, mert pont, hogy eleve a logikád szerint 8x sávot kap. Tehát especiel nála tökmindegy, hogy lesz-e bifubricate vagy sem, mert ha 16x sávot is kapna, akkor se lenne gyorsabb, mintha 8x sávot kap...

-

Nem tudom hogy kerül az m-ITX ide, mert az teljesen más tészta.

Ott a kis méret miatt eleve több PCB réteg kell, hogy a különféle vezetékelést kellő zavarvédelemmel meg tudják oldani. Nem véletlen, hogy a "normális" m-ITX deszkák zömmel 10 rétegűek, de legalább 8 (persze van 12 rétegű is...).A nagyobb (m-ATX, ATX, EATX) deszkáknál bőven van hely szétrakni az részelemeket, hogy egy rétegen több eszköz vezetékelését is megoldják.

A másik oldala meg az, hogy az m-ITX erősen rétegtermék, így szűk piacon kell eladni a portékát, nem véletlen, hogy még a nagy gyártóknak is csak 2, esetleg 3 m-ITX deszkájuk van egy platformra. Ezek mind árfelhajtó tényezők, szóval hogy nincs olcsó m-ITX AM5 deszka, az cseppet sem meglepő....

-

válasz

deathcrow42

#16

üzenetére

deathcrow42

#16

üzenetére

Nem hiszem, hogy ilyesmi lenne az AMD célja, az okot Te is leírtad: drága.

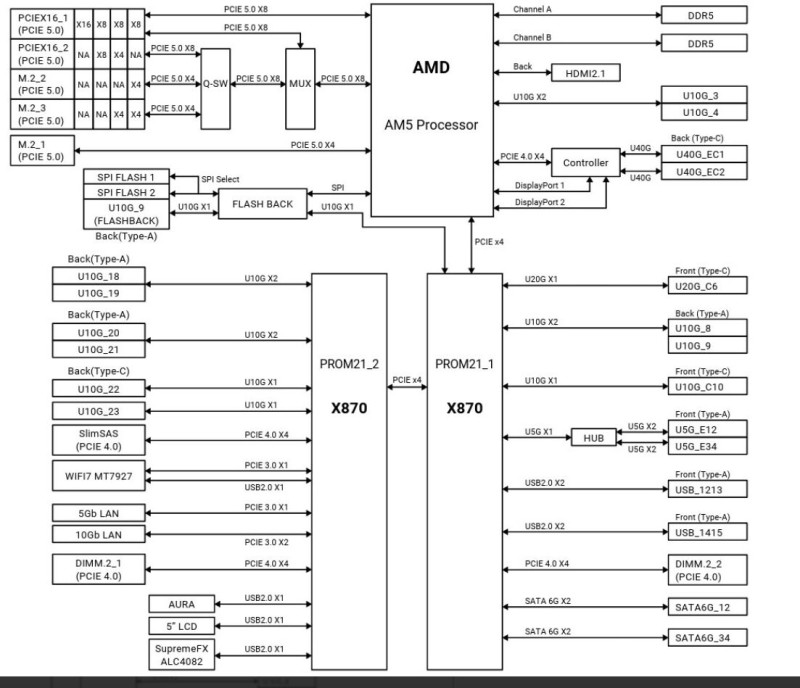

Az átlagos felhasználónak a VGA x16 sáv* mellé kell x4 sáv az M.2 SSD mellé és még x4 van az extrákra, mint az USB4 vezérlő. Szóval nagyon maximálisan még 4 sáv extrát tudok elképzelni, lehet még az se lesz, inkább, ahogy írtam, a SoC felé menő négy sávot Gen5 szintre fejlesztik.

Ez az átlagos usernek untig elég, aki meg sok PCI-express sávot, még 4+ M.2 SSD-t akar, vegyen Threadrippert...*: Igazából az átlagos felhasználónak nem kell x16 Gen5 sáv se a VGA-hoz. x8 is untig elég a felső középkategóriás (RTX **70) kártyákig. Nem véletlen, hogy az AMD és az Nvidia is eleve x8 sávos vezérlőt rak az alsóbb szériában...

Ezt amúgy a gyártók is tudják, nem ördögtől való a bifubricate, csak az elitista felhasználók sírnak miatta, mert sírni kell...

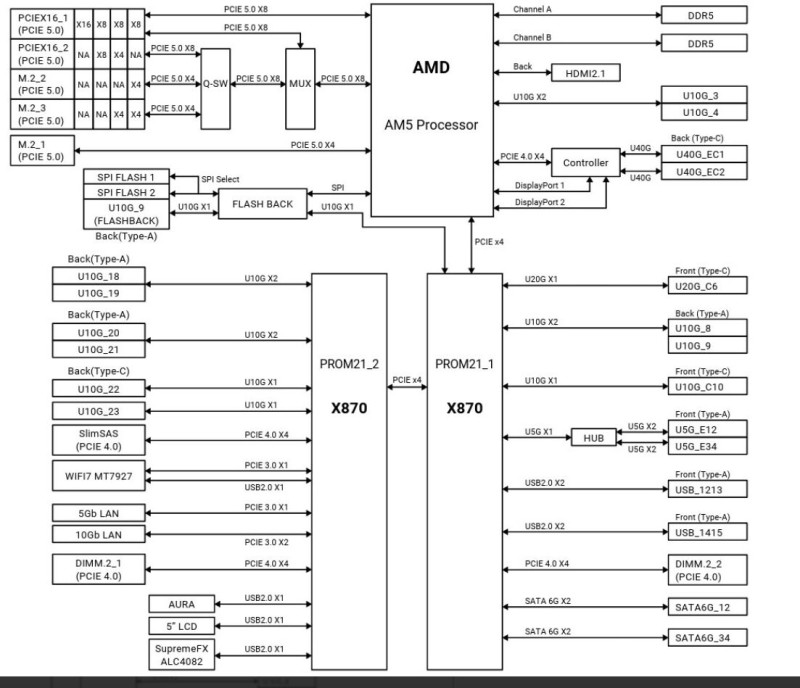

A csúcs ASUS ROG deszka felosztása is tükrözi ezt:

-

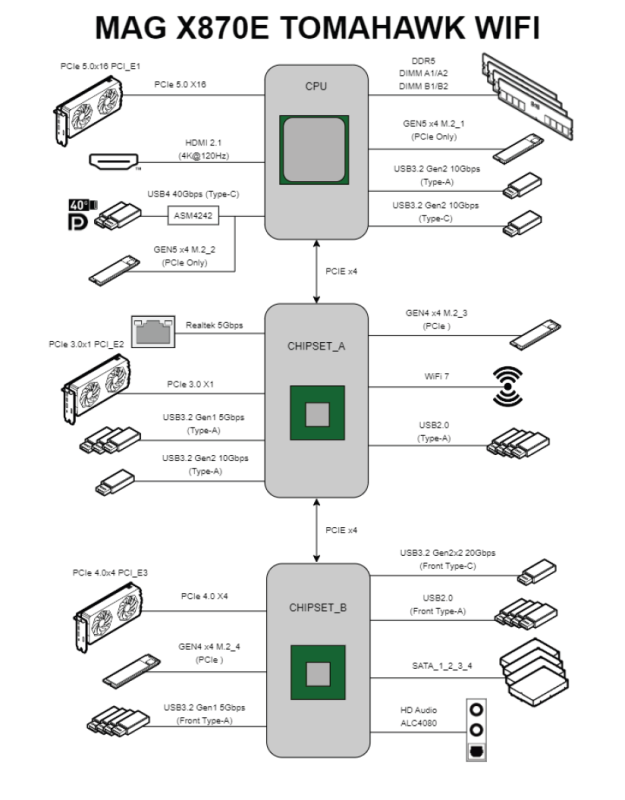

A gyakorlatban azt, hogy van 24 szabadon használható sáv a 'Raphael' és 'Granite Ridge' esetén.

-x16 sáv ment a VGA-nak

-x4 sáv az első M.2 NVME csatinak

-x4 sáv maradt egyebekre, ami pl. egy x4-es PCI-Express vagy M.2 NVME csati lehetettAmíg ezt az X670(E) és B650(E) esetén meg tehették, most zömmel az alsó x4 sáv elmegy az USB4-es vezérlőnek. A plusz CPU-ra kötött M.2 csatikat pedig így jobbára az x16-os VGA csatoból választják le.

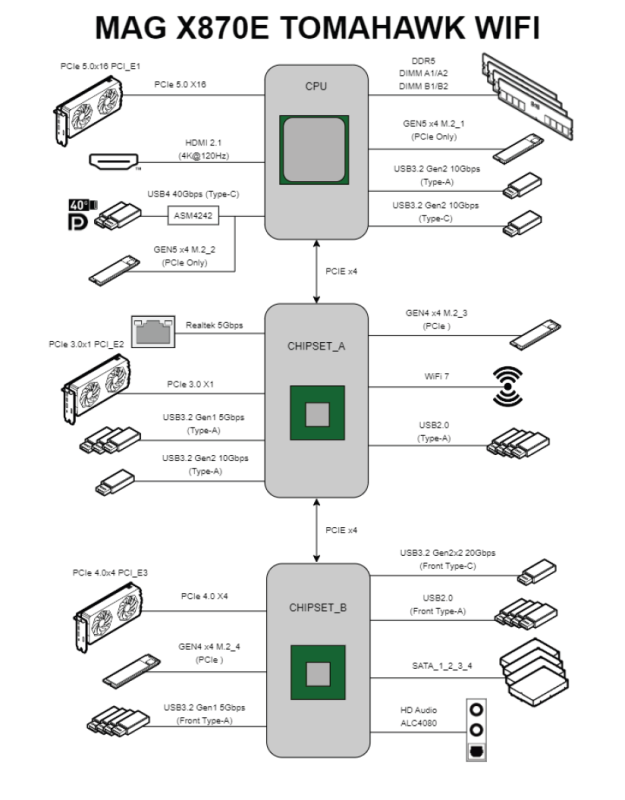

Az MSI látva ezt inkább úgy döntött, hogy ők az USB4 vezérlőt teszik választóra, tehát választhatsz, hogy USB4-est akarsz, vagy egy második Gen5 x4-es NMVE csatit...

Ha az USB4-et kihasználod, akkor ez nem hátrány, hanem feature.

Ha az USB4-et nem szeretnéd, de a plusz CPU-ból érkező sávokat igen, akkor viszont alaposan át kell nézni az alaplapok manualját, hogy ki tudd választani a Neked megfelelőt.Amit pedig írtam, a fenti ábrán tökéletesen látható: a CPU-ból x4 sáv megy az alaplapi SoC felé, de az is Gen5 lenne, csak az SoC-n Gen4-es vezérlő van. Tehát ha a következő Promontory vezérlőn ezt lecserélik Gen5-re, akkor hirtelen duplázódik a leosztható sávszélesség, amit a rá kötött eszközök felhasználhatnak...

-

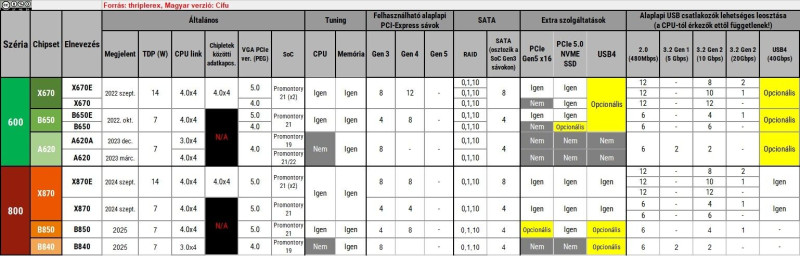

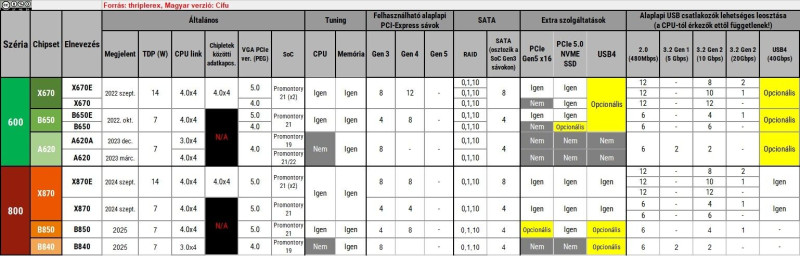

Pont ez a bajom. Az AMD marketing azt súlykolta anno is, hogy B650E vs. B650... nem lesz Gen5-ös PCI-Express-ed. Aztán sok esetben mégis lett.

Megpróbálják eladni a B850-et és az X870(E)-t jobbnak eladni, mint a B650(E) és X670(E), holott az USB4 és esetleg a Wifi7 képességért cserébe kevesebb valósan felhasználható PCI-Express sávot kapsz (zömmel kettő-négy sáv megy a 24-ből az USB4 vezérlőnek...). -

Őőőő... A "chipset" szón én picit mosolygok. De értem mire gondolsz.

A B650, B650E, X670, X670E, B850, X870, X870E alaplapokban Promontory 21 chip található. Az X670(E) és az X870E esetén két darab, a többiben egy.

Az X870(E) esetén kötelező az USB4 verzérlő, ez volt "az" újdonság a 800-as szérián. Meg esetleg a WiFi7 vezérlő még ilyesmi.

A Promontory 21 esetén 4x Gen4-es PCI-Express sávon csatlakozik a CPU felé.

Én igencsak időszerűnek érezném a SoC felé a Gen5-ös PCI-Express sávokra váltást, ezzel ugye duplázódik a SoC / SoC-ok felé a sávszélesség. Tehát igen, egy következő Promontory SoC (Prom23?) várható gondolom.

Plusz a CUDIMM memória modul támogatás lenne még lényeges gondolom, de az alaplapi SoC-től független.

-

[Új pletyka a MLID forrásból]

A lényeg, hogy a Zen6 esetén a CCD-n lévő magok sebessége 6GHz felett várható, sőt, a csúcs peociknál akár a 7GHz-et is elérheti.

Feltehetően nem az X3D változatokra vonatkozik ez, de az N2X node olyan előrelépés lesz, ami ezt vetíti előre.... -

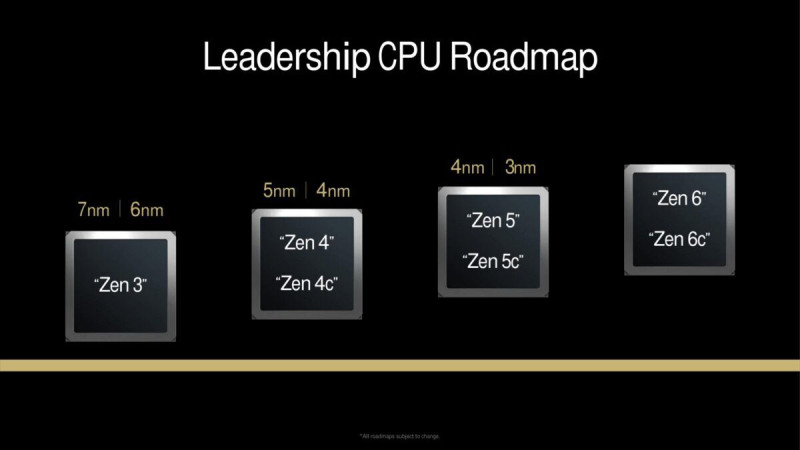

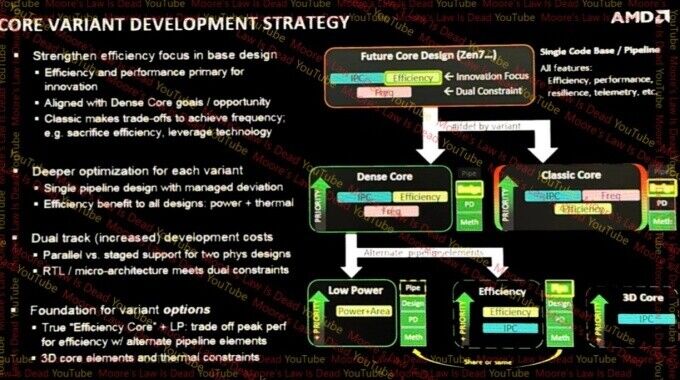

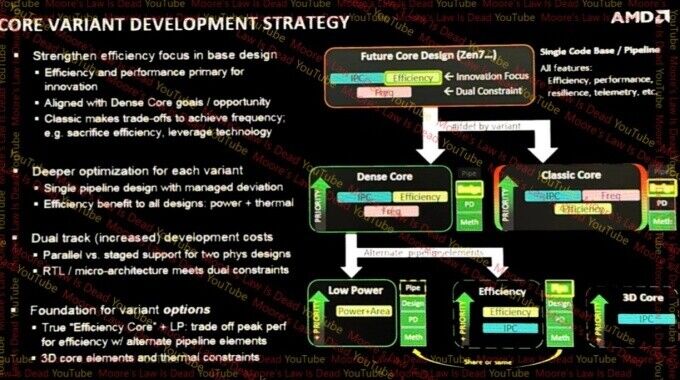

Ez ugyan Zen7 téma, de a várható fejlesztési tervekről szóló pletyka jött ki a Moore's Law is Dead csatornán.

A lényeg összefoglalva:

Az AMD Fejlesztési stratégiája a Zen4-nél elindult két lépcsős (Zen4 és a kicsivel kisebb területen dolgozó, de alapvetően hasonló IPC-re képes Zen4c) szintet folytatták a Zen5 esetén is, újabban a "Dense" jelölést kapta a "c" változat.Viszont már a Zen6-nál hallottunk egy Low-Power magról, a Zen7 esetén pedig ezek mellé még bejön egy Efficiency változat is, tehát tovább bővül a magok típusa.

Tehát a magok:

Classic: Teljesítmény (IPC, Frekvencia) a prioritás, a hatékonyság kevésbé, de jelen van.

Dense: IPC és hatékonyság priorizált változat, ahol a frekvenciát második sorba tették.

Low Power: Energiahatékonyság és minél kisebb terület a fő csapás, IPC és frekvencia szóba se kerül.

Efficiency: Energiahatékonyságra helyezi a hangsúlyt, másod sorban az IPC-t még figyelembe veszi.

-

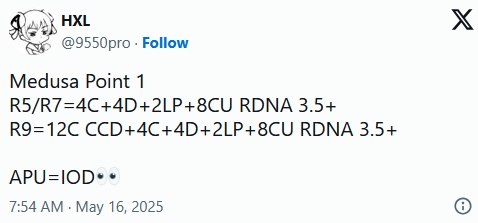

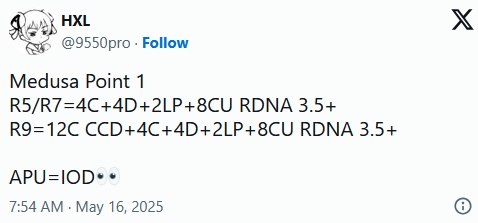

Új pletyka az Medusa Point 1 APU-ról (alapvetően laptopokba, de desktopba is várható):

A Ryzen 5 / 7 APU-k esetén:

4x "classic" Zen6 mag

4x "dense" Zen6c

2x Low-Power mag

8 CU RDNA 3.5+ GPUA Ryzen 9 esetén a fentiek mellé még ejön egy 12 "classic" Zen6 magot tartalmazó CCD.

A pletykaforrás lényegi kérdése az, hogy az IoD egyben egy komplett APU lenne?

-

Új pletykák (Moore Law"s Dead forrás):

Olympic Ridge & Gator Range:

- AM5 + FL1 foglalat (az FL1 az AM5 integrált mobilalaplapi változata)

- TSMC N2X gyártástechnológia a CCD chipletleknél

- TMSC N3P és/vagy N6 gyártástechnológia az IOD chipleteknél (dobták a Samsungot?)

- 128 bites DDR5 memória vezérlő

- Az N3P változatú IOD-n 2 magos Zen5 Low Power mag

- Az N6 változatú IOD-n nincs Zen5 LP mag.

- Mind az N3P, mind az N6 féle IOD esetén felmerült, hogy iGPU nélkül változat is érkezik

- Még formálódik az IOD világ, de lehet, hogy az olcsóbb procik N6 IOD-val érkeznek, a drágábbak kapján majd az N3P féle változatot.

- A Zen5 LP magok (Zen5c? - Cifu) pluszba érkeznek, tehát 1 CCD változatnál legfeljebb 12 Zen6 + 2 Zen5 LP mag lesz a procin, vagyis 14 magos lehet. A 2 CCD-nél logikusan 26 mag (2x12 Zen6 és 2 Zen5LP).A Zen5 LP magok IOD-s elhelyezése érdekes vonulat, egyfelől mert frappáns, másfelől mert így közvetlenül a memóriavezérlő mellett lesz (milyen jó poén lesz, amikor az AIDA64 memória benchmark megpróbálja ezt lekövetni

), ugyanakkor nem fér hozzá a CCD L1/L2/L3 cache-hez.

), ugyanakkor nem fér hozzá a CCD L1/L2/L3 cache-hez. -

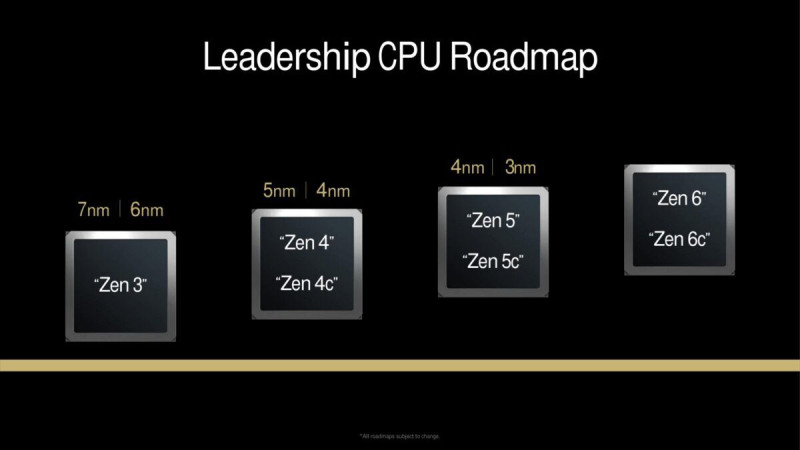

Még sok téren inkább pletyka szint, de nyissuk meg ezt is.

Zen6 ("Morpheus") architektúra az AMD Zen családjának "következő" lépése.

A Desktop változat (ami eme topicra tartozik) kódneve "Olympic Ridge", míg a mobil változaté "Medusa Point".

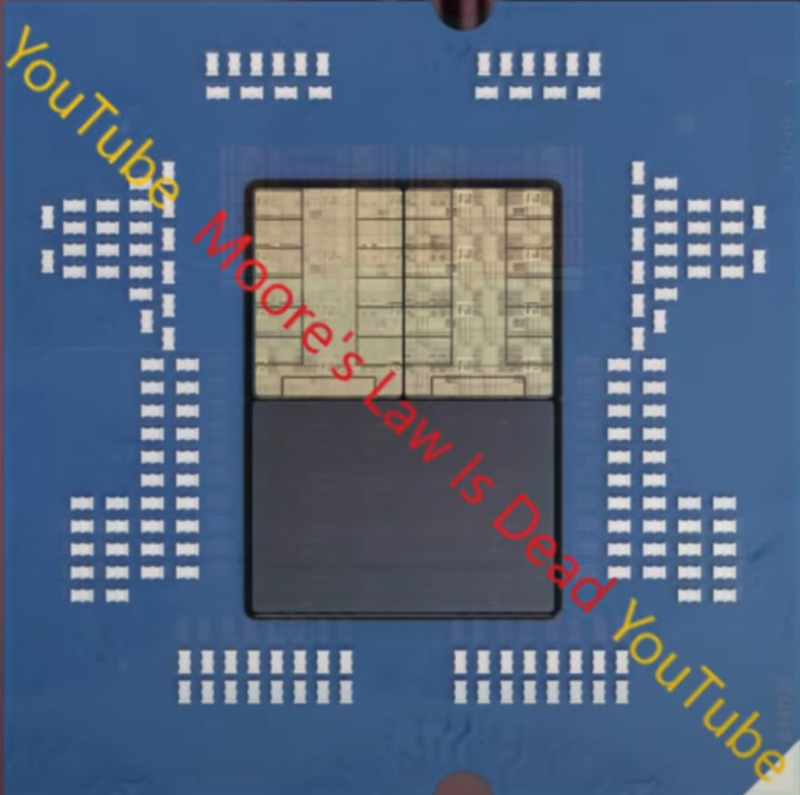

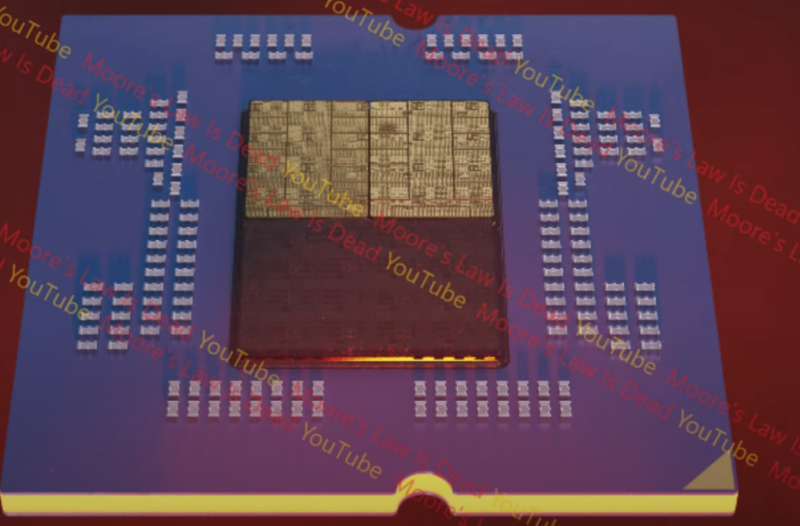

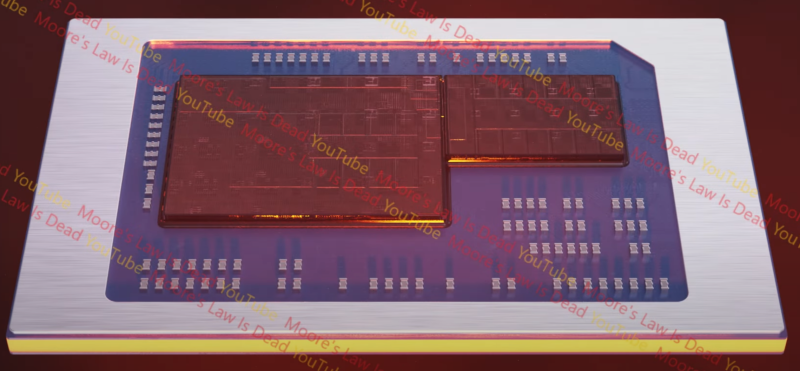

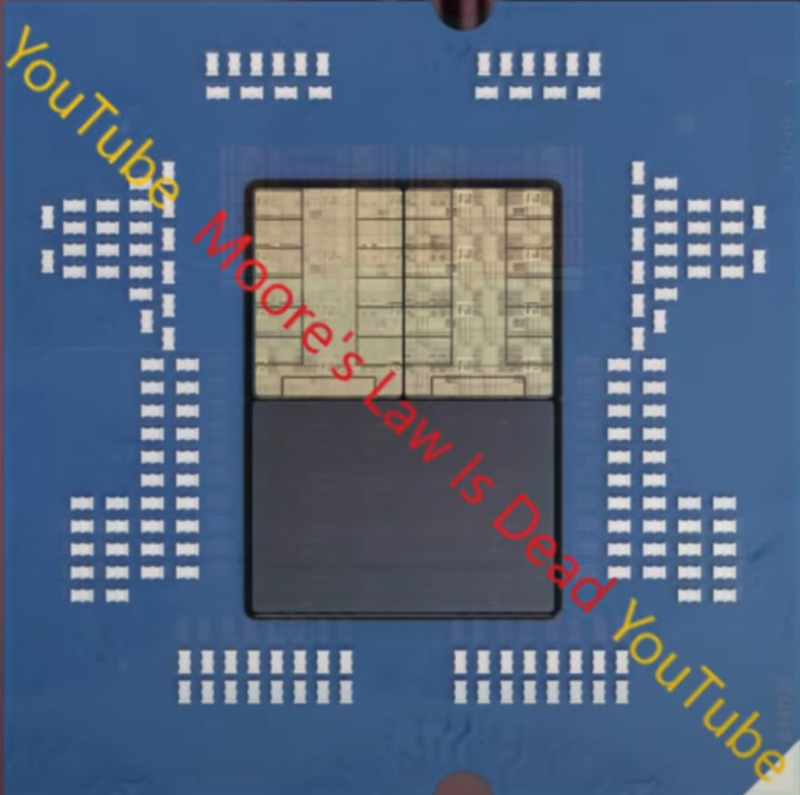

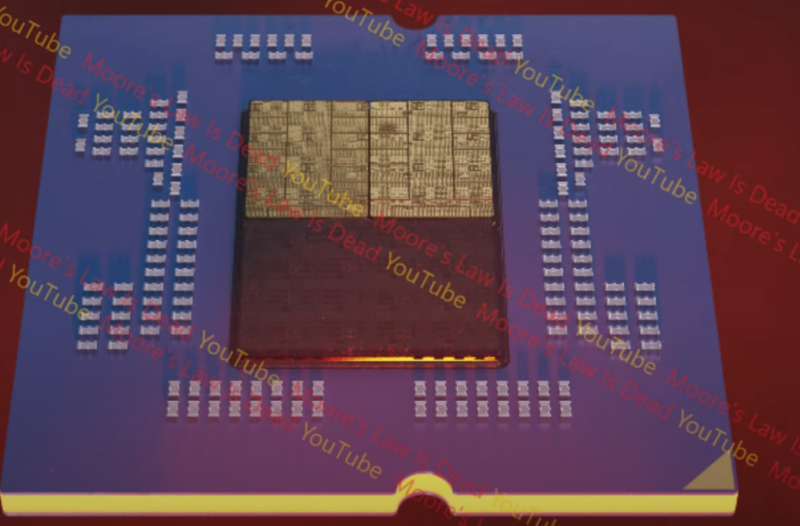

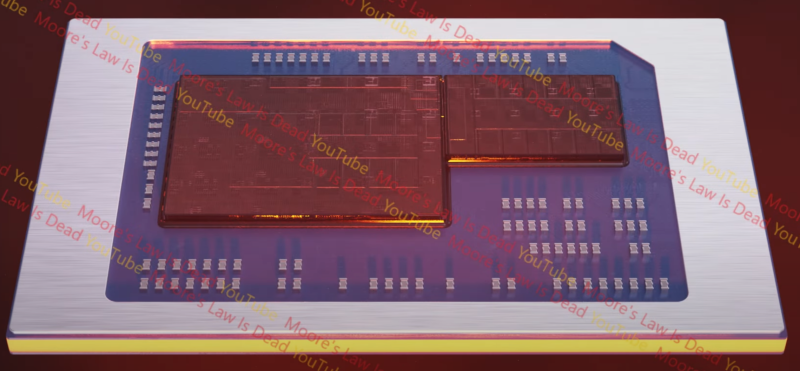

A Moore's Law is Dead videón kiszivárgott képen több érdekesség is látható. Egyfelől a két CCD közvetlenül egymás mellett van, nincs közöttük egy rés, mint a Zen4 esetén. A másik érdekesség, hogy a CCD-ken 2x6 CPU mag látható, tehát egy CCD-n (a Zen arch indulása óta) először nőtt a magszám 8-ról 12-re (nem számítva persze a Zen4c változatot, ami csak szerverre jött ki).

A harmadik az, hogy a hírek szerint orvosolják az eddigi kialakítás egyik fő problémáját, mely szerint a két CCD között nincs közvetlen kapcsolat. Eddig mindig az IOD (ismertebb talán a SOC elnevezés) chiplethez kapcsolódtak, ez pedig a CCD-k közötti adatmozgatást "némileg" lassította. A közvetlen kapcsolatot egy 2.5D-s interposer teszi lehetővé, és persze az, hogy közvetlenül egymás mellé kerültek a CCD-k.

A CCD-k várhatóan 3nm-es, feltehetően a TSMC N3P node-ján készülnek majd.Ugyan a Desktop érdekel minket első sorban, de ami érdekesség, hogy a mobil fronton is a chiplet design felé fordulna az AMD, legalábbis a kiszivárgott "Medusa Point" képen egy CCD látható egy IO chiplet mellett, ami nagyobb, mint a desktop IOD (több GPU CU van rajta).

Az IOD-ről annyit hallani, hogy várhatóan a Samsung 4LPP node-ján készül majd, és cél a stabil DDR5-8000+ RAM sebesség biztosítása, illetve az új technológiák, mint a CUDIMM támogatása.

A platform terén sok találgatás megy, de mivel az AMD-nek a Zen4 -> Zen5 váltáshoz 22 hónap kellett, és azt már [sokszor leírták, hogy az AM5 támogatása 2027-ig biztos meglesz] , ami még legalább egy ekkora távlat, így talán hihetünk a képeknek, amelyen AM5 tokozás látható.

A kérdés persze leginkább a mikor?

A jelen állás szerint 2026 végén, 2027 elején várhatjuk a Zen6-ot...

Új hozzászólás Aktív témák

Hirdetés

- ÚJ, 27% számlás! AMD Ryzen 7 7800X3D (96M Cache, up to 5 GHz) Processzor! BeszámítOK

- Eladó ÚJ Intel Core i3 10105F bontatlan dobozos processzor 3 év garancia 27% áfa

- AMD Ryzen 5 5600X - Új, 3 év garancia - Eladó!

- Ritkaság! Csere-Beszámítás! Intel I9 13900KS Processzor!

- AMD Ryzen 7 5700X3D - BOX - Új, 3 év garancia - Eladó!

- Telefon Felvásárlás!! iPhone 14/iPhone 14 Plus/iPhone 14 Pro/iPhone 14 Pro Max

- AKCIÓ! Apple Mac mini 2020 M1 8GB 256GB SSD számítógép garanciával, hibátlan működéssel

- Apple iPhone SE 2020 64GB, Kártyafüggetlen, 1 Év Garanciával

- ÁRGARANCIA! Épített KomPhone i7 14700KF 32/64GB RAM RTX 5090 32GB GAMER PC termékbeszámítással

- LG 32GS95UE - 32" OLED / UHD 4K / 240Hz - 480Hz & 0.03ms / 1300 Nits / NVIDIA G-Sync / AMD FreeSync

Állásajánlatok

Cég: PCMENTOR SZERVIZ KFT.

Város: Budapest

), ugyanakkor nem fér hozzá a CCD L1/L2/L3 cache-hez.

), ugyanakkor nem fér hozzá a CCD L1/L2/L3 cache-hez.