- Samsung Galaxy S23 és S23+ - ami belül van, az számít igazán

- Android szakmai topik

- Minden a BlackBerry telefonokról és rendszerről

- Android alkalmazások - szoftver kibeszélő topik

- Samsung Galaxy S24 - nos, Exynos

- Asus ROG Phone 8 Pro - az élet nem csak játék és mese

- Honor Magic6 Pro - kör közepén számok

- Samsung Galaxy A54 - türelemjáték

- iOS alkalmazások

- Telekom mobilszolgáltatások

Hirdetés

-

Megbírságolták a Razert a Zephyr maszkok miatt

ph A cég elég olcsón megússza az ügyfelei félrevezetését, de az üdvözlendő, hogy az Egyesült Államok hatóságai nem siklottak el az ügy felett.

-

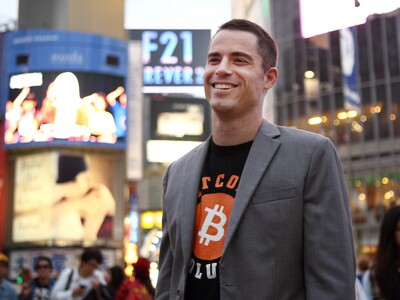

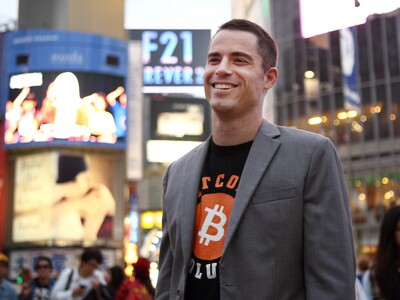

Letartóztatták a bitcoin-Jézust

it Amerikai adókerülés vádjával, Spanyolországban tartóztatták le a bitcoin-Jézusként ismert Roger Vert.

-

Mindent megtudtunk az új Nokia 3210-ről

ma Részletes képek, specifikációk és euróban megadott ár is van a legendás modell újraélesztett verziójához.

-

Mobilarena

OLVASD VÉGIG ALAPOSAN MIELŐTT ÚJ HOZZÁSZÓLÁST ÍRNÁL!!!

Új hozzászólás Aktív témák

-

Raymond

félisten

''A P4 azzal szúrta el, hogy az eleve lassú főmemória mellé egy nevetséges L1Dcache került. Itt a főmemória pöpec, de az L1 csak elégséges. Két szálnak kevés lenne. ''

Sebessegre vagy kapacitasra gondolsz? Ha nagyobb lenne vagy meg lasabb lenne vagy komoly valtoztatasokat igenyelne a front-end hogy a mostani 3 ciklust megtartsak.

Szerk: Az irasodbol ugy ertelmeztem hogy itt=K8 vagy K10.

[Szerkesztve]Privat velemeny - keretik nem megkovezni...

-

P.H.

senior tag

macro-op cache: nem gondoltam a disszipációra, csak arra, hogy a ciklus-utasítások megspórolnának pár stage-t (gyorsulás). Az x86 beállt olyan 60-120W fogyasztásra, beleférnek növelő lépések, más, csökkentő lépések mellett.

elágazás-kezelés: úgy gondoltam, hogy csak azon elágazásoknak futna le mindkét ága, amelyek rendelkeznek az előző pontban említett prefix-szel, tehát a fordító jelezné, hogy IF-ELSE-ről van szó, és a displacement 8 bit-es (ezt elírtam), szóval a L1 instruction cache-re sem nehezedne számottevően nagyobb nyomás. Cikluselágazásokra teljesen megfelelő az eddigi becslési módszer. Ilyen vegyes megoldást még nem láttam sehol, és az random adatokon alapuló IF-ELSE-t minden mai x86 architechure is megsínyli. A prefix ötletét meg az Intel branch hint prefix-éből vettem.

Hyper-Threading: nem hiszem, hogy (prioritással kiegészítve) szélesíteni kellene a jelenlegi architectúrát. A fő cél az execution unit-ok lehető legteljesebb kihasználása, úgy, hogy ne egymás elől vegyék el a sávszélességet, bármilyen áron. Felsoroltam az elgondolásaimat, nem biztos, hogy mindegyik megfér egymás mellett.

El tudom képzelni, hogy egy high-class szál mondjuk az ő CPU-idejében főszálként fusson, máskor pedig mint másodszál, ami kihasználja a szabad execution portokat és macro-op helyeket. Persze, ez akkor hoz nagy teljesítménynövekedést hogy igaz, amit sejtek, hogy decode után (azaz utasítássorrendben) AMD-nél macroop-hármasoknál nincs vízszintes mozgás, tehát egy IMUL eax,ebx; IMUL ecx,edx; ADD esi,edi két hármasra fordul, ugyanúgy, mint egy ADDSS xmm0,xmm1; ADDSS xmm2,xmm3; MULPS xmm4,xmm5 (The instruction control unit takes the three macro-ops per cycle from the early decoders and places them in a centralized, fixed-issue reorder buffer). Ezesetben a tripletek teli vannak üres helyekkel (bubbles), amit ki lehetne tölteni.

Az Intel a cache mellett azzal is elszúrta, hogy a HyperThreading-et a PPro óta megjelent ''legkeskenyebb'' micro-architektúráján alkalmazta (4 port, shared INT/FPU).

[Szerkesztve]Arguing on the Internet is like running in the Special Olympics. Even if you win, you are still ... ˙˙˙ Real Eyes Realize Real Lies ˙˙˙

Új hozzászólás Aktív témák

A topikban az OFF és minden egyéb, nem a témához kapcsolódó hozzászólás gyártása TILOS!

Az ide nem illő hozzászólások topikja:[link]

MIELŐTT LINKELNÉL VAGY KÉRDEZNÉL, MINDIG OLVASS KICSIT VISSZA!!

A topik témája:

Az AMD éppen érkező, vagy jövőbeni új processzorainak kivesézése, lehetőleg minél inkább szakmai keretek között maradva.

- Crypto Trade

- Politika

- Samsung Galaxy S23 és S23+ - ami belül van, az számít igazán

- Sub-ZeRo: Euro Truck Simulator 2 & American Truck Simulator 1 (esetleg 2 majd, ha lesz) :)

- Folyószámla, bankszámla, bankváltás, külföldi kártyahasználat

- Az Apple megszerezné a klubvilágbajnokság közvetítési jogait

- Honda topik

- Autós topik

- Opel topik

- Hogy is néznek ki a gépeink?

- További aktív témák...

Állásajánlatok

Cég: Promenade Publishing House Kft.

Város: Budapest

Cég: Ozeki Kft.

Város: Debrecen