- Képeken az egyik kameráját elvesztő Sony Xperia 10 VI

- Apple iPhone 15 Pro Max - Attack on Titan

- Egyre közelebb a Poco F6 startja

- Mindent megtudtunk az új Nokia 3210-ről

- iPhone topik

- Újabb Samsungok telepíthetik a Galaxy AI-t

- Bemutatkozott a Moto G32 4G

- Nothing Phone 2a - semmi nem drága

- Xiaomi 13T és 13T Pro - nincs tétlenkedés

- Poco X6 Pro - ötös alá

Hirdetés

-

AMD Radeon undervolt/overclock

lo Minden egy hideg, téli estén kezdődött, mikor rájöttem, hogy már kicsit kevés az RTX2060...

-

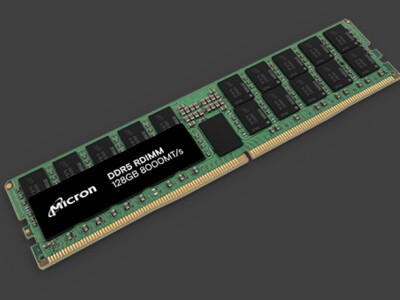

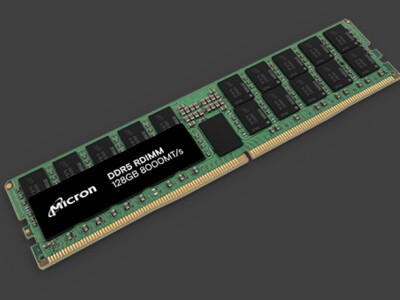

Alacsony fogyasztású, 128 GB-os szervermemóriát kínál a Micron

ph Az új RDIMM TSV technológia alkalmazása nélkül éri el a címben említett tárkapacitást.

-

Sokat fogyaszt az AI, egyre több az adatközpont, kell az atomenergia

it Az AI-t kiszolgáló adatközpontok olyan nagy energiaigénnyel bírnak, hogy egyre több atomenergiára van szükség.

Új hozzászólás Aktív témák

-

#25954560

törölt tag

erdekes lenne tudni, hogy van-e valami specialis cache-management megoldasa az AMD-nek, amivel a juzer tudja kicsit finomhangolni a mukodeset. igaz az Intel CAT(cache allocation technology) sem lett atuto siker. valoszinuleg a cache mennyisege miatt amugy sem lesz teleszemetelve, szoval nincs szukseg arra h eroltessem valami adat bentmaradasat. azert cache-en allokalni memoriat eleg utos lehetne

van par erdekes info Junius 1-rol az anandtech oldalan:

- This technology will be productized with 7nm Zen 3-based Ryzen processors. Nothing was said about EPYC.

- Those processors will start production at the end of the year. No comment on availability, although Q1 2022 would fit into AMD's regular cadence.

- This V-Cache chiplet is 64 MB of additional L3, with no stepped penalty on latency. The V-Cache is address striped with the normal L3 and can be powered down when not in use. The V-Cache sits on the same power plane as the regular L3.

- The processor with V-Cache is the same z-height as current Zen 3 products - both the core chiplet and the V-Cache are thinned to have an equal z-height as the IOD die for seamless integration

- As the V-Cache is built over the L3 cache on the main CCX, it doesn't sit over any of the hotspots created by the cores and so thermal considerations are less of an issue. The support silicon above the cores is designed to be thermally efficient.

- The V-Cache is a single 64 MB die, and is relatively denser than the normal L3 because it uses SRAM-optimized libraries of TSMC's 7nm process, AMD knows that TSMC can do multiple stacked dies, however AMD is only talking about a 1-High stack at this time which it will bring to market.

Új hozzászólás Aktív témák

ph Friss részleteket osztott meg a világga, az EPYC termékcsaláddal kapcsolatban jól értesült ExecutableFix nevű Twitter felhasználó.

- Xbox Series X|S

- Kerékpárosok, bringások ide!

- Képeken az egyik kameráját elvesztő Sony Xperia 10 VI

- Apple iPhone 15 Pro Max - Attack on Titan

- Sokat fogyaszt az AI, egyre több az adatközpont, kell az atomenergia

- Egyre közelebb a Poco F6 startja

- Fujifilm X

- Mindent megtudtunk az új Nokia 3210-ről

- A fociról könnyedén, egy baráti társaságban

- CASIO órák kedvelők topicja!

- További aktív témák...

- MacMini M1

- Beszámítás! ASRock H310CM i7 8700 16GB DDR4 500GB SSD RTX 2070 Super 8GB CM Q500L CM 500W

- Beszámítás! ASUS Prime B450M R5 5600 16GB DDR4 256GB SSD 1TB HDD RTX 2080 Super Rampage SHIVA TT 600

- Beszámítás! GIGABYTE H610M i5 12400F 32GB DDR4 1TB SSD RTX 3060Ti 8GB MONTECH AIR 1000 Seasonic 650W

- Beszámítás! GIGABYTE H610M i5 13400F 32GB DDR4 1TB SSD RTX 3070Ti 8GB TT Core V71 Be Quiet! 650W

Állásajánlatok

Cég: Ozeki Kft.

Város: Debrecen

Cég: Promenade Publishing House Kft.

Város: Budapest